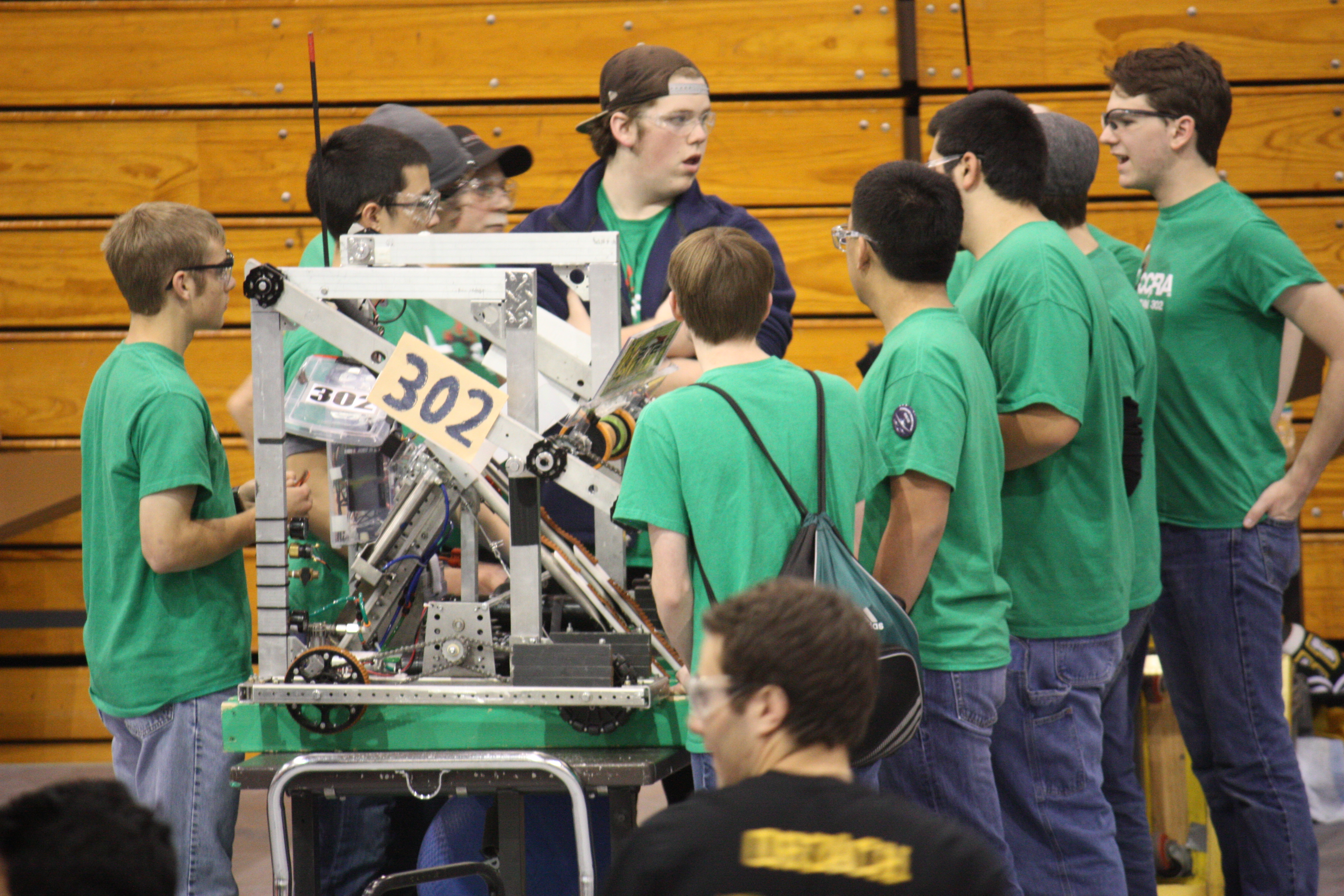

Experts React The Legacy Of Lake Orions Award Winning Robotics Program Team 302 Orion

I'm having a bit of difficulty understanding pipeline hazards, especially data hazards and how we can use stall cycles and data forwarding to resolve these hazards. Also, we do not allow results to be written to the $0 register so, in the event that an instruction uses $0 as its destination (which is legal), we should not forward the result (because it won’t. Some set of instructions are given such that functionality of every unit.

Mark Garrett on LinkedIn Congratulations Lake Orion Robotics Team!!

Compare the source registers of the instruction in the decode stage with the destination register of the uncommitted instructions. One way of handling raw data hazards is to stall the pipeline until the required destination register is updated in the reg file. Read after write (raw), write after read (war), write after write (waw), and read after read (rar).

There are four types of data dependencies:

Forwarding now, we’ll introduce some problems that data hazards can cause for our pipelined processor, and show how to handle them with forwarding. The processor supports basic arithmetic, logic, memory, and control operations, and is suitable for educational purposes and basic cpu architecture experiments. This requires freezing the execution of instructions that have. Today we’ll introduce some problems that data hazards.

— so we can execute up to five instructions in any clock cycle, with each instruction in a different stage and using different hardware.